![]() Анализ и управление состоянием (AVT)

Анализ и управление состоянием (AVT)

![]() Измерение по трем точкам (VTR)

Измерение по трем точкам (VTR)

![]() Выбор аналогового сигнала (SF3)

Выбор аналогового сигнала (SF3)

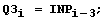

SEL = INk , (k = 0,1), если IG = k.

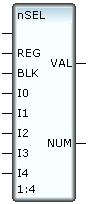

Выход NUM этого блока равен номеру одного из входов I0…I4, значение которого передается на выход VAL. Коммутацией управляют входы REG и BLK. Если REG = 0, на выход VAL передается наименьшее из входных значений, если REG = 1 – наибольшее.

Первые 5 битов числа, поданного на вход BLK, определяют участие входов в выборе. Если бит равен 0, соответствующий ему по номеру вход рассматривается, 1 – игнорируется.

Если входом BLK заблокированы все 5 сигнальных входов, NUM = -2.

Этот блок возвращает большее из входных значений.

Этот блок возвращает меньшее из входных значений.

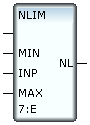

Этот блок клиппирует входной сигнал (вход INP), если его значение выходит за границы заданного диапазона:

Q = MAX, если INP > MAX

Q = MIN, если INP < MIN

Q = INP, если MIN <= INP <= MAX

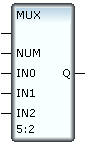

Q = INk , (k = 0,1,2), если NUM = k.

Если NUM принимает другое значение, то на текущем такте пересчета значение выхода Q не изменяется.

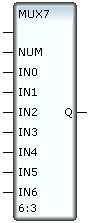

Q = INk , (k = 0,1…6), если NUM = k.

Если NUM принимает другое значение, то на текущем такте пересчета значение выхода Q не изменяется.

NL = 1, если INP > MAX (на вход INP подается анализируемое значение)

NL = 0, если MIN <= INP <= MAX

NL = 2, если INP < MIN

Данный блок реализует звено чистого запаздывания:

где i – номер текущего такта пересчета блока.

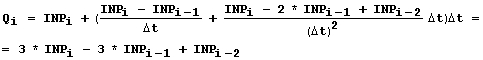

Этот блок реализует функцию экстраполяции входного значения по первой и второй производным. Выходу Q присваивается предполагаемое значение входа INP на следующем такте пересчета. Вычисление значения выхода осуществляется по следующей формуле:

где i – номер текущего такта пересчета.

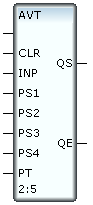

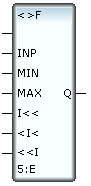

Анализ и управление состоянием (AVT)

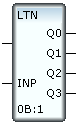

По результатам анализа значения, поданного на вход INP, блок последовательно изменяет состояние управляемого объекта.

При подаче 1 на вход CLR выходы блока обнуляются, и он прекращает свою работу.

При подаче 0 на вход CLR блок переходит в рабочий режим, при этом на один такт пересчета бит 0 выхода QS принимает значение 1.

На первом этапе работы блок сравнивает значения входов INP и PS1. Если INP<>PS1 в течение PT тактов пересчета, биты 0 и 8 выхода QE принимают значение 1 (QE=16#101). Установившиеся значения выходов остаются неизменными до тех пор, пока значения INP и PS1 не станут равными. Когда INP=PS1, бит 1 QS принимает значение 1 на один такт пересчета, а байт 1 QS принимает постоянное значение 1 (т.е. на один такт пересчета QS принимает значение 16#102, а затем – постоянное значение 16#100). Выход QE вначале обнуляется, а по окончании текущего интервала из PT тактов пересчета его биты 0 и 9 принимают постоянное значение 1 (QE=16#201). На этом первый этап работы блока завершается, а значения выходов (QS=16#100 и QE=16#201) остаются неизменными до тех пор, пока не выполнится условие INP=PS2.

Следующие этапы аналогичны первому, т.е. когда INP становится равным PS<k+1>, где k = 1,2,3 – номер последнего завершенного этапа, QS изменяет свое значение: бит с номером (k+1) принимает значение 1 на один такт пересчета, а байт 1 принимает постоянное значение k+1. Выход QE вначале обнуляется, а по окончании текущего интервала из PT тактов пересчета его биты 0 и k+9 (бит (k+1) байта 1) принимают постоянное значение 1 (по завершении последнего (четвертого) этапа и последующем истечении PT тактов пересчета QE=2).

Таким образом:

![]() в байте 1 QS формируется код нового

состояния объекта (1,2,3,4);

в байте 1 QS формируется код нового

состояния объекта (1,2,3,4);

![]() импульс в i-ом (i=1,2,3,4) бите

QS указывает на завершение i-ого этапа;

импульс в i-ом (i=1,2,3,4) бите

QS указывает на завершение i-ого этапа;

![]() ненулевое значение QE индицирует превышение

времени исполнения этапа, заданное PT. При этом:

ненулевое значение QE индицирует превышение

времени исполнения этапа, заданное PT. При этом:

![]() номер установленного в 1 бита байта 1 QE

равен номеру последнего завершенного этапа (после завершения

четвертого этапа байт 1 QE принимает значение 0);

номер установленного в 1 бита байта 1 QE

равен номеру последнего завершенного этапа (после завершения

четвертого этапа байт 1 QE принимает значение 0);

![]() байт 0 QE равен 2 после завершения этапа 4

и 1 – после завершения любого другого этапа.

байт 0 QE равен 2 после завершения этапа 4

и 1 – после завершения любого другого этапа.

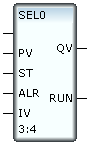

Этот блок управляет несколькими (до 8) однотипными агрегатами для получения заданной выработки.

На вход PV данного блока подается задание на выработку. Вход ST используется для ввода данных о состоянии агрегатов. Каждый его бит описывает состояние соответствующего агрегата (0 - выключен, 1 - включен). Вход ALR используется для указания работоспособности агрегатов. Каждый бит этого входа описывает соответствующий агрегат (0 - работоспособен, 1 - неисправен). На последний вход (IV) подается производительность одного агрегата.

На выходе QV формируется значение предполагаемой выработки. Оно вычисляется как сумма производительностей агрегатов, для которых сформированы команды на включение. Эти команды формируются на выходе RUN. Каждый бит данного выхода управляет соответствующим агрегатом (0 - выключить, 1 - включить). Формирование этих команд осуществляется с учетом текущего состояния и работоспособности агрегатов для обеспечения следующего условия: предполагаемая выработка должна быть не меньше заданной.

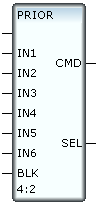

Данный блок имеет шесть входов для команд управления (IN1…IN6) и один вход блокирования команд (BLK).

Из входов IN1…IN6 выбирается наименьший по номеру вход, который не блокирован и имеет ненулевое значение. Значение такого входа передается на выход CMD, а его номер – на выход SEL.

Блокировать можно только входы IN3…IN6. Управляет блокировкой вход BLK. Его биты 0-3 блокируют команду 1, поданную на соответствующий вход, биты 4-7 – команду 2, биты 8-11 – команду 3. Младшему биту в каждой четверке соответствует вход IN3, а старшему – IN6. Блокирование осуществляется по равенству бита единице. Например, чтобы блокировать команду 3, поданную на вход IN4, нужно подать на вход BLK значение 29 (512).

Назначение других битов BLK:

![]() Бит 12 (0x1000) – если 1: обнулить CMD;

Бит 12 (0x1000) – если 1: обнулить CMD;

![]() Бит 13 (0x2000) – если 1: обнулить SEL;

Бит 13 (0x2000) – если 1: обнулить SEL;

![]() Бит 14 (0x4000) –

Бит 14 (0x4000) –

![]() Бит 15 (0x8000) – блокировать все команды по

IN1 и IN2;

Бит 15 (0x8000) – блокировать все команды по

IN1 и IN2;

![]() Бит 16 (0x10000) – если 1: блокировать битами 8-11

команду -1 (вместо команды 3);

Бит 16 (0x10000) – если 1: блокировать битами 8-11

команду -1 (вместо команды 3);

![]() Бит 17 (0x20000) – если 1: копировать 0 на выход

при подаче 4 на соответствующий вход;

Бит 17 (0x20000) – если 1: копировать 0 на выход

при подаче 4 на соответствующий вход;

![]() Бит 18 (0x40000) – если 1: умножить CMD на

0x400 (для ZDV и KLP);

Бит 18 (0x40000) – если 1: умножить CMD на

0x400 (для ZDV и KLP);

![]() Бит 19 (0x80000) – если 1: обнулить выходы и

отключить блок.

Бит 19 (0x80000) – если 1: обнулить выходы и

отключить блок.

Данный блок позволяет формировать произвольные значения в зависимости от интервала, в который попадает анализируемое значение, поданное на вход INP.

Если INP < MIN, то Q = I<<

Если MIN <= INP <= MAX, то Q = <I<

Если INP > MAX, то Q = <<I

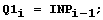

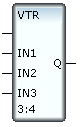

Измерение по трем точкам (VTR)

Значение выхода этого блока вычисляется по следующей формуле:

Qi = (IN1 + IN2 + IN3 + Qi-1 - MIN – MAX) / 2

где

i – номер текущего такта пересчета;

IN<k> – значения входов (квазипостоянные величины);

MIN – минимальное из IN1, IN2, IN3 и Qi-1;

MAX – максимальное из IN1, IN2, IN3 и Qi-1.

Таким образом, выходное значение формируется плавно, без скачка.

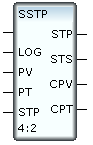

Данный блок переводит управляемый объект в состояние, которое выбирает в соответствии со значениями своих входов.

Входы блока:

LOG – управляющий вход. Допустимые значения – 0 и 1;

PT – уставка таймера (задается в тактах пересчета);

PV – уставка счетчика событий. Под событием здесь понимается изменение значения входа LOG с 0 на 1;

STP – код следующего состояния. При равенстве этого параметра 0 код следующего состояния равен коду текущего состояния, увеличенному на единицу.

Выходы блока:

CPT – текущее значение таймера (в тактах пересчета). Выход CPT обнуляется при переходе в новое состояние;

CPV – текущее значение счетчика событий. Выход CPV обнуляется при переходе в новое состояние;

STP – код текущего состояния;

STS – код условия, по которому выбрано текущее состояние.

Переход в новое состояние, заданное входом STP, производится при выполнении любого из двух следующих условий:

![]() CPV=PV, т.е. если значение входа

LOG изменилось с 0 на 1 PV раз;

CPV=PV, т.е. если значение входа

LOG изменилось с 0 на 1 PV раз;

![]() CPT=PT, т.е. если истекло заданное

время.

CPT=PT, т.е. если истекло заданное

время.

Выход STS принимает следующие значения:

0 – если LOG=0 и еще не произошло ни одного перехода;

1 – если LOG=0, а текущее состояние выбрано по условию CPV=PV;

2 – если LOG=0, а текущее состояние выбрано по условию CPT=PT;

16 – если LOG=1 и еще не произошло ни одного перехода;

17 – если LOG=1, а текущее состояние выбрано по условию CPV=PV;

18 – если LOG=1, а текущее состояние выбрано по условию CPT=PT.

Подача отрицательного значения на вход PV, PT или STP останавливает работу блока и формирует на выходе CPV, CPT и STP соответственно значение |PV|, |PT| и |вход STP|. После снятия отрицательных значений со входов блок отрабатывает свои функции в соответствии с установленными значениями на выходах.

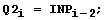

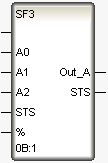

Выбор аналогового сигнала (SF3)

Биты 0-2 входа STS – достоверность соответственно значений A0-A2 (0 – достоверно, 1 – недостоверно).

Если A0-A2 недостоверны, Out_A не меняется и устанавливается бит 0 выхода STS.

Если из A0-A2 достоверно только одно значение, оно записывается в Out_A.

Если из A0-A2 достоверны два значения, в Out_A записывается их среднее арифметическое.

Если A0-A2 достоверны:

![]() если бит 8 входа STS не установлен,

Out_A=M, где M – медиана

(вычисляется по A0-A2). Кроме того, вычисляются

величины di =

(Ai-M)/M.

При di >

% устанавливаются соответственно биты 8, 9 и 10 выхода

STS;

если бит 8 входа STS не установлен,

Out_A=M, где M – медиана

(вычисляется по A0-A2). Кроме того, вычисляются

величины di =

(Ai-M)/M.

При di >

% устанавливаются соответственно биты 8, 9 и 10 выхода

STS;

![]() если бит 8 входа STS установлен, блок

работает по аналогичному алгоритму, но дополнительно вычисляется

сумма значений A0-A2, из которой затем вычитаются

значения, для которых di > %.

Скорректированная таким образом сумма делится на N (число

значений, для которых di < %),

и полученный результат записывается в

Out_A.

если бит 8 входа STS установлен, блок

работает по аналогичному алгоритму, но дополнительно вычисляется

сумма значений A0-A2, из которой затем вычитаются

значения, для которых di > %.

Скорректированная таким образом сумма делится на N (число

значений, для которых di < %),

и полученный результат записывается в

Out_A.

Если установлен бит 9 входа STS, значение битов 12-15 выхода STS индицирует N.

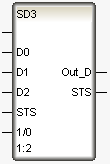

Биты 0-2 входа STS – достоверность соответственно значений D0-D2 (0 – достоверно, 1 – недостоверно).

Если D0-D2 недостоверны, Out_D не меняется и устанавливается бит 0 выхода STS.

Если из D0-D2 достоверно только одно значение, оно записывается в Out_D.

Если из D0-D2 достоверны два значения (Dk и Dm):

![]() если бит 0 входа 1/0 равен 0,

то Out_D = Dk OR

Dm

если бит 0 входа 1/0 равен 0,

то Out_D = Dk OR

Dm

![]() если бит 0 входа 1/0 равен 1,

то Out_D = Dk AND

Dm

если бит 0 входа 1/0 равен 1,

то Out_D = Dk AND

Dm

Если D0-D2 достоверны, то Out_D = S = (D0 & D1) | (D0 & D2) | (D1 & D2) (S равно 0 или 1 в зависимости от того, каких значений больше в D0-D2). Далее S сравнивается с D0-D2, при неравенстве устанавливаются соответственно биты 8-10 выхода STS. Если установлен бит 9 входа 1/0, значение битов 12-15 выхода STS индицирует число значений, равных S.