![]() Импульс по переднему фронту (rTRIG)

Импульс по переднему фронту (rTRIG)

![]() Импульс по заднему фронту (fTRIG)

Импульс по заднему фронту (fTRIG)

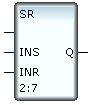

![]() Триггер с приоритетом по установке (SR)

Триггер с приоритетом по установке (SR)

![]() Триггер с приоритетом по сбросу (RS)

Триггер с приоритетом по сбросу (RS)

![]() Комбинированный счетчик (CTUD)

Комбинированный счетчик (CTUD)

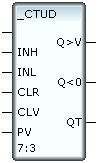

![]() Комбинированный счетчик 2 (_CTUD)

Комбинированный счетчик 2 (_CTUD)

![]() Импульс произвольной длительности (TP)

Импульс произвольной длительности (TP)

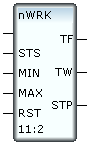

![]() Сторожевой таймер мотора (nWRK)

Сторожевой таймер мотора (nWRK)

Импульс по переднему фронту (rTRIG)

Этот блок формирует прямоугольный импульс длиной в один такт пересчета при изменении значения младшего разряда INP с 0 на 1.

Импульс по заднему фронту (fTRIG)

Выход QF принимает значение 1 на один такт пересчета при изменении значения входа INP с любого положительного на 0.

Триггер с приоритетом по установке (SR)

Выход Q изменяет свое значение с 0 на 1 при изменении значения входа INS с 0 на любое положительное (при этом значение входа INR может быть любым неотрицательным).

Для сброса выхода в 0 нужно подать 0 на вход INS и любое положительное значение на вход INR.

Триггер с приоритетом по сбросу (RS)

Выход Q изменяет свое значение с 0 на 1, если INS > 0 и INR = 0.

Для сброса выхода в 0 нужно подать любое положительное значение на вход INR.

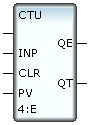

Функцией данного блока является подсчет количества тактов пересчета, в течение которых значение контролируемой величины (вход INP) было отлично от 0, и сравнение этого количества с заданной уставкой. Вход CLR используется для смещения текущего значения счетчика (выход QT), вход PV – для задания уставки, а выход QE показывает результат сравнения значения счетчика с уставкой.

Ниже индекс i обозначает номер текущего такта пересчета блока.

При CLRi = 0 и QTi < PVi:

если INPi <> 0 , то QTi = QTi –1 + 1, в противном случае QTi = QTi –1

При CLRi > 0:

QTi = CLRi - 1 и вне зависимости от PVi и INPi счетчик останавливается.

Если QTi > PVi, то QEi = 1 (при этом счетчик останавливается), в противном случае QEi = 0.

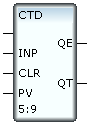

Этот блок аналогичен блоку CTU, но реализует обратный счетчик.

Контролируемая величина подается на вход INP. Вход CLR используется для смещения текущего значения счетчика (выход QT), вход PV – для задания начального значения счетчика, выход QE показывает результат сравнения значения счетчика с 0.

Ниже индекс i обозначает номер текущего такта пересчета блока.

При CLRi = 0:

если INPi <> 0 , то QTi = QTi –1 - 1, в противном случае QTi = QTi –1

При CLRi <> 0:

QTi = PVi – (CLRi – 1) и вне зависимости от INPi счетчик останавливается

Если QTi < 0, то QEi = 1 (при этом счетчик останавливается), в противном случае QEi = 0.

Данный блок аналогичен триггеру с приоритетом по установке (блок SR). Отличие заключается в том, что установка 1 на выходе осуществляется с задержкой на один такт. Сброс выхода в 0 осуществляется на том же такте, на котором одновременно INR <> 0 и INS = 0.

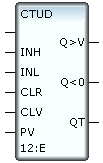

Комбинированный счетчик (CTUD)

Этот блок сочетает в себе функции нарастающего и убывающего счетчиков.

Наличие ненулевого значения на входе INH увеличивает значение счетчика на 1 (выход QT), наличие ненулевого значения на входе INL – уменьшает. Вход INH имеет более высокий приоритет, чем INL, поэтому при ненулевых значениях обоих входов блок работает как нарастающий счетчик.

Вход PV задает максимальное значение для нарастающего счетчика и начальное значение для убывающего счетчика.

Ниже индекс i обозначает номер текущего такта пересчета блока.

Нарастающий счетчик:

При CLRi = 0 и QTi < PVi:

если INHi <> 0, то QTi = QTi –1 + 1, в противном случае QTi = QTi –1

При CLRi > 0:

QTi = 0 и счетчик останавливается.

Если QTi > PVi, то Q>Vi = 1 (при этом счетчик останавливается), в противном случае Q>Vi = 0.

Убывающий счетчик:

При CLVi = 0:

если INLi <> 0 , то QTi = QTi –1 - 1, в противном случае QTi = QTi –1

При CLVi <> 0:

QTi = PVi и счетчик останавливается

Если QTi < 0, то Q<0i = 1 (при этом счетчик останавливается), в противном случае Q<0i = 0.

Комбинированный счетчик 2 (_CTUD)

Этот блок аналогичен блоку CTUD за одним исключением: он останавливается, если одновременно INH <> 0 и INL <> 0.

Импульс произвольной длительности (TP)

Этот блок предназначен для формирования импульсов единичной амплитуды и заданной длительности.

Импульс формируется на выходе QI при изменении значения входа INP с 0 на любое положительное. Длительность импульса в тактах пересчета задает вход PT. Выход QT индицирует число тактов, прошедших с начала формирования импульса.

Перед формированием очередного импульса нужно обнулить выход QT (для этого нужно подать 0 на вход INP).

При изменении значения входа INP с 0 на любое ненулевое выход QI принимает значение 1 с задержкой в PT тактов пересчета, при этом выход QT индицирует число тактов, прошедших с момента изменения INP.

Чтобы обнулить выходы QI и QT, нужно подать 0 на вход INP.

Если INP <> 0, то QI = 1, QT = 0.

При изменении значения входа INP с ненулевого на 0 выход QI принимает значение 0 с задержкой в PT тактов пересчета, при этом выход QT индицирует число тактов, прошедших с момента изменения INP.

Сторожевой таймер мотора (nWRK)

Этот блок контролирует время работы устройства типа "двигатель", управляемого блоком MOTOR. Блок nWRK может быть использован для выключения мотора через определенный промежуток времени.

Вход STS блока nWRK нужно соединить с выходом STS блока MOTOR. При STS=1 или 17 (мотор работает) увеличивается значение выходов TF и TW. Эти выходы показывают соответственно общее время работы мотора и время работы с момента последнего включения. Единицы измерения времени задаются значением битов 4-7 входа RST: 0 – дни, 1 – часы, 2 – минуты, 3 – секунды.

Если бит 0 RST равен 1, обнуляются выходы, указанные последующим битами при их равенстве 1: бит 1 – выход TF, бит 2 – выход TW, бит 3 – выход STP.

Если значение выхода TW (время работы с момента последнего включения) превышает значение входа MAX, то выходу STP присваивается значение 1. Этот сигнал может использоваться для выключения мотора.

Если STP=0, TW принимает значение 0 на том же такте пересчета, на котором STS становится отлично от 1 или 17.

Если STP=1, а STS становится отлично от 1 или 17 (2, 18, 10 или 26), то STP=0 на этом же такте пересчета, а TW принимает значение 0 спустя MIN (если STS принимает другие значения, то STP=0 и TW=0 на этом же такте пересчета). Значение входа MIN не должно превышать 127.

Соответствующие биты 32-разрядных INS, INR и Q образуют 32 триггера с приоритетом по установке (см. описание блока SR).