![]() Экспоненциальное сглаживание (SMTH)

Экспоненциальное сглаживание (SMTH)

![]() Зона нечувствительности (DZONE)

Зона нечувствительности (DZONE)

![]() Настройки параметров задвижек и клапанов (SdV)

Настройки параметров задвижек и клапанов (SdV)

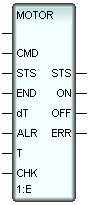

![]() Управление устройством типа 'двигатель' (MOTOR)

Управление устройством типа 'двигатель' (MOTOR)

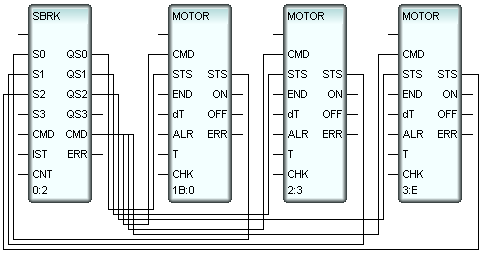

![]() Управление группой устройств типа 'двигатель' (SBRK)

Управление группой устройств типа 'двигатель' (SBRK)

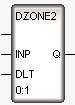

![]() Зона нечувствительности 2 (DZONE2)

Зона нечувствительности 2 (DZONE2)

![]() Реальное дифференцирование (RDIF)

Реальное дифференцирование (RDIF)

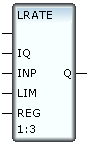

Экспоненциальное сглаживание (SMTH)

Этот блок выполняет суммирование с весом:

Q = IQ*(1 – 1/PK) + INP/PK

Если выход Q соединен со входом IQ, блок выполняет экспоненциальное сглаживание сигнала, поданного на вход INP. При этом коэффициент сглаживания (вход PK) должен быть больше 1.

Этот блок с соединенными выходом Q и входом IQ ограничивает скорость изменения сигнала, поданного на вход INP. Максимально допустимое изменение сигнала задается входом LIM. Выходное значение формируется следующим образом.

IF |INP-IQ|>LIM THEN Q:=IQ+SIGN(INP-IQ)*LIM

ELSE Q:=INP

Вход REG задает режим работы блока:

0 – ограничение скорости в соответствии с описанным выше алгоритмом;

1 – запрет увеличения;

2 – запрет уменьшения;

3 – фиксация значения выхода.

Этот блок с соединенными выходом Q и входом IQ фильтрует небольшие изменения (например, шумы дискретизации) сигнала, поданного на вход INP. Величина порога задается входом LIM. Алгоритм формирования выходного значения выглядит следующим образом.

IF |INP-IQ|<LIM THEN Q:=IQ

ELSE Q:=INP

Этот блок с соединенными выходом Q и входом IQ фильтрует случайные броски сигнала, поданного на вход INP. Максимально допустимое изменение сигнала задается входом LIM. Выходное значение формируется следующим образом (i обозначает текущий такт пересчета).

IF |INPi-IQi|<=LIM THEN Qi:=INPi

ELSE IF |INPi–1 - IQi-1|<=LIM THEN Qi:=IQi

ELSE Qi:=INPi

Таким образом, значение входа INP передается на выход, если его изменение на текущем такте пересчета не превысило LIM, в противном случае выход не изменяется. Если на следующем такте пересчета разность INP и Q опять превысила LIM, то на выход передается значение INP.

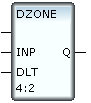

Зона нечувствительности (DZONE)

Данный блок работает как блок APERT с IQ = 0:

IF |INP|<DLT THEN Q:=0

ELSE Q:=INP

Функцией данного блока является формирование единичного выходного сигнала при переходе входного значения (INP) через заданную границу (PV) с учетом значения гистерезиса (DLT).

IF INP>PV+DLT THEN Q:=1

IF INP<PV-DLT THEN Q:=0

Этот блок воспроизводит на выходе входное значение. Однако при каждом изменении входного значения величина выхода обнуляется на один такт и только на следующем становится равной входу. Как следствие, выходное значение всегда равно нулю, если входной сигнал изменяется на каждом такте пересчета.

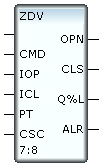

Данный блок управляет устройством типа "задвижка". Он анализирует следующие цифровые сигналы (0 или 1): сигналы концевых выключателей открытия, закрытия и муфты, сигнал электрической части (привода) и сигнал о наличии электрического напряжения (например, на соленоиде).

Для управления блоком могут использоваться как потенциальные, так и импульсные команды; в последнем случае команда отрабатывается по переднему фронту импульса.

Вход CMD предназначен для подачи команд управления. Потенциальные команды:

![]() 0 – остановить;

0 – остановить;

![]() 1 – открыть;

1 – открыть;

![]() 2 – закрыть;

2 – закрыть;

![]() 17 – открыть и сбросить ошибки;

17 – открыть и сбросить ошибки;

![]() 18 – закрыть и сбросить ошибки;

18 – закрыть и сбросить ошибки;

![]() 20 – остановить и сбросить ошибки.

20 – остановить и сбросить ошибки.

Импульсные команды:

![]() импульс в бите 0 CMD – открыть;

импульс в бите 0 CMD – открыть;

![]() импульс в бите 1 CMD – закрыть;

импульс в бите 1 CMD – закрыть;

![]() импульс в бите 2 CMD – остановить.

импульс в бите 2 CMD – остановить.

При одновременной подаче импульсов в биты CMD: CMD=3 – закрыть, CMD=5 или 7 – остановить.

При выполнении команд открытия/закрытия на выходе OPN формируется сигнал открытия (бит 0 равен 1), на выходе CLS – сигнал закрытия (бит 0 равен 1).

На вход IOP подаются следующие сигналы:

![]() бит 0 (0x1) – сигнал концевого выключателя

открытия (если бит 6 CSC не установлен: 1 – открыто

полностью, 0 – закрыто или открыто не полностью);

бит 0 (0x1) – сигнал концевого выключателя

открытия (если бит 6 CSC не установлен: 1 – открыто

полностью, 0 – закрыто или открыто не полностью);

![]() бит 3 или 8 (0x8 или 0x100) – сигнал электрической

части (привода) (0 – не работает, 1 – работает);

бит 3 или 8 (0x8 или 0x100) – сигнал электрической

части (привода) (0 – не работает, 1 – работает);

![]() бит 2 или 9 (0x4 или 0x200) – сигнал о наличии

напряжения: 0 – норма, 1 – авария.

бит 2 или 9 (0x4 или 0x200) – сигнал о наличии

напряжения: 0 – норма, 1 – авария.

На вход ICL подаются следующие сигналы:

![]() бит 0 (0x1) – сигнал концевого выключателя

закрытия (если бит 6 CSC не установлен: 1 – закрыто

полностью, 0 – открыто или закрыто не полностью);

бит 0 (0x1) – сигнал концевого выключателя

закрытия (если бит 6 CSC не установлен: 1 – закрыто

полностью, 0 – открыто или закрыто не полностью);

![]() бит 1 (0x2) – сигнал концевого выключателя муфты

(если бит 6 CSC не установлен: 1 – закрыто полностью, 0 –

открыто или закрыто не полностью);

бит 1 (0x2) – сигнал концевого выключателя муфты

(если бит 6 CSC не установлен: 1 – закрыто полностью, 0 –

открыто или закрыто не полностью);

![]() биты 3 и 8 (0x8 и 0x100) – аналоги битов 3 и 8

IOP;

биты 3 и 8 (0x8 и 0x100) – аналоги битов 3 и 8

IOP;

![]() бит 2 или 9 (0x4 или 0x200) – аналоги битов 2 и 9

IOP.

бит 2 или 9 (0x4 или 0x200) – аналоги битов 2 и 9

IOP.

Если на ICL ничего не подано, то ICL = IOP & 6.

Вход PT используется для задания времени хода задвижки (в секундах). Его значение должно быть немного больше реального времени хода. По значению PT и времени, прошедшему с момента подачи команды, блок вычисляет текущее положение задвижки и выводит полученное значение на выход Q%L:

Q%Ln=Q%L0

100*(n-1)*t/PT

100*(n-1)*t/PT

где Q%L0 – положение задвижки при подаче команды, Q%Ln – положение задвижки спустя n тактов пересчета после подачи команды, t – период пересчета в секундах, знак "+" соответствует закрытию, знак "-" – открытию (т.е. выход индицирует процент закрытия задвижки). В приведенной формуле учтено, что при подаче команды блок останавливается на 1 такт для сброса управляющего сигнала на выходе OPN или CLS (даже если этот сигнал не сформирован).

Сигналы концевых выключателей имеют более высокий приоритет по сравнению с вычисленным положением задвижки, т.е. если при открытии (закрытии) включился концевой выключатель открытия (концевые выключатели закрытия и муфты), блок ZDV считает задвижку полностью открытой (закрытой) и Q%L=0 (100) на следующем такте пересчета.

Установленные в 1 биты входа CSC задают следующие режимы работы блока:

![]() бит 0 (0x1) – блокирование контроля концевого

выключателя открытия;

бит 0 (0x1) – блокирование контроля концевого

выключателя открытия;

![]() бит 1 (0x2) – блокирование контроля концевого

выключателя закрытия;

бит 1 (0x2) – блокирование контроля концевого

выключателя закрытия;

![]() бит 2 (0x4) – блокирование контроля концевого

выключателя муфты;

бит 2 (0x4) – блокирование контроля концевого

выключателя муфты;

![]() бит 3 (0x8) – принудительное присваивание выходу

Q%L значения 0 ("открыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

бит 3 (0x8) – принудительное присваивание выходу

Q%L значения 0 ("открыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

![]() бит 4 (0x10) – принудительное присваивание выходу

Q%L значения 100 ("закрыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

бит 4 (0x10) – принудительное присваивание выходу

Q%L значения 100 ("закрыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

![]() бит 5 (0x20) – выход из аварийной ситуации. При

возникновении аварийной ситуации при открытии/закрытии

соответствующие выходы (OPN и CLS) принимают значение

0 (процедура прерывается), и блок ZDV останавливается. Если

в режиме остановки ошибку устранить (т.е. задать корректное

сочетание значений входов), выполнение процедуры не возобновится, и

признак аварии, сформированный на выходе ALR, сохранится.

Для сброса признака аварии и возобновления выполнения процедуры

нужно установить данный бит в 1. При установке бита 5 возможна

одновременная установка бита 3 (0x8) или бита 4 (0x10) для

выполнения соответствующих функций (одновременная установка битов

3-5 равнозначна установке одного бита 5). При выходе из аварийной

ситуации:

бит 5 (0x20) – выход из аварийной ситуации. При

возникновении аварийной ситуации при открытии/закрытии

соответствующие выходы (OPN и CLS) принимают значение

0 (процедура прерывается), и блок ZDV останавливается. Если

в режиме остановки ошибку устранить (т.е. задать корректное

сочетание значений входов), выполнение процедуры не возобновится, и

признак аварии, сформированный на выходе ALR, сохранится.

Для сброса признака аварии и возобновления выполнения процедуры

нужно установить данный бит в 1. При установке бита 5 возможна

одновременная установка бита 3 (0x8) или бита 4 (0x10) для

выполнения соответствующих функций (одновременная установка битов

3-5 равнозначна установке одного бита 5). При выходе из аварийной

ситуации:

![]() если задвижка была открыта/закрыта по времени, а

затем остановлена при закрытии/открытии, то автоматически

Q%L=50;

если задвижка была открыта/закрыта по времени, а

затем остановлена при закрытии/открытии, то автоматически

Q%L=50;

![]() если задвижка была закрыта по времени, а затем

возникла ошибка 4, то автоматически Q%L=

%SdV

(%SdV

– процент закрытия, соответствующий таймауту концевого

выключателя);

если задвижка была закрыта по времени, а затем

возникла ошибка 4, то автоматически Q%L=

%SdV

(%SdV

– процент закрытия, соответствующий таймауту концевого

выключателя);

![]() если задвижка была открыта по времени, а затем

возникла ошибка 5, то автоматически Q%L=

100-%SdV;

если задвижка была открыта по времени, а затем

возникла ошибка 5, то автоматически Q%L=

100-%SdV;

![]() после ошибки 6 или 2 – задвижка автоматически

устанавливается в положение "открыто";

после ошибки 6 или 2 – задвижка автоматически

устанавливается в положение "открыто";

![]() после ошибки 7 или 3 – задвижка автоматически

устанавливается в положение "закрыто";

после ошибки 7 или 3 – задвижка автоматически

устанавливается в положение "закрыто";

![]() после ошибки 10 – автоматически

Q%L=Q%L+2;

после ошибки 10 – автоматически

Q%L=Q%L+2;

![]() после ошибки 11, 12 или 13 – автоматически

Q%L=Q%L-2;

после ошибки 11, 12 или 13 – автоматически

Q%L=Q%L-2;

![]() после других ошибок – попытка (1 такт)

идентификации положения задвижки;

после других ошибок – попытка (1 такт)

идентификации положения задвижки;

![]() бит 6 (0x40) – инверсные сигналы концевых

выключателей открытия, закрытия и муфты;

бит 6 (0x40) – инверсные сигналы концевых

выключателей открытия, закрытия и муфты;

![]() бит 7 (0x80) – перевод в режим отслеживания

состояния задвижки по концевым выключателям (аварийные ситуации не

контролируются). Этот режим индицируется значением 15 байта 1

(0x0F00) выхода ALR);

бит 7 (0x80) – перевод в режим отслеживания

состояния задвижки по концевым выключателям (аварийные ситуации не

контролируются). Этот режим индицируется значением 15 байта 1

(0x0F00) выхода ALR);

![]() бит 8 (0x100) – см. ниже описание ошибки 14;

бит 8 (0x100) – см. ниже описание ошибки 14;

![]() бит 9 (0x200) – импульсные управляющие сигналы

открытия (бит 0 OPN), закрытия (бит 0 CLS) и

остановки (бит 2 или 9 OPN), длина импульса определяется

битами 12-14. При отключении концевого выключателя соответствующий

импульс сбрасывается;

бит 9 (0x200) – импульсные управляющие сигналы

открытия (бит 0 OPN), закрытия (бит 0 CLS) и

остановки (бит 2 или 9 OPN), длина импульса определяется

битами 12-14. При отключении концевого выключателя соответствующий

импульс сбрасывается;

![]() бит 10 (0x400) – блокирование команды

открытия;

бит 10 (0x400) – блокирование команды

открытия;

![]() бит 11 (0x800) – блокирование команды

закрытия;

бит 11 (0x800) – блокирование команды

закрытия;

Если команда открытия (закрытия) блокируется битом 10 (11) STS в момент выполнения, задвижка останавливается.

![]() биты 12-14 (маска 0x7000) – эти биты задают длину

управляющего импульса. Длина импульса в секундах рассчитывается по

следующей формуле:

биты 12-14 (маска 0x7000) – эти биты задают длину

управляющего импульса. Длина импульса в секундах рассчитывается по

следующей формуле:

0.5 + [(CSC & 0x7000) >> 12] + K

K задается с помощью ключа VLVAIMP в файле *.cnf. По умолчанию K = 2с, эта константа не может превышать время, соответствующее 31 такту пересчета блока;

![]() бит 15 (0x8000) – 1 – управляющий сигнал остановки

вырабатывается в бите 2 OPN, 0 – в бите 9 OPN. В

режиме импульсных управляющих сигналов (установлен бит 9):

бит 15 (0x8000) – 1 – управляющий сигнал остановки

вырабатывается в бите 2 OPN, 0 – в бите 9 OPN. В

режиме импульсных управляющих сигналов (установлен бит 9):

![]() генерация импульса остановки зависит от бита

22;

генерация импульса остановки зависит от бита

22;

![]() в течение импульса остановки команды

открытия/закрытия игнорируются;

в течение импульса остановки команды

открытия/закрытия игнорируются;

![]() бит 16 (0x10000) – индикация процента открытия

задвижки вместо процента закрытия на выходе

Q%L;

бит 16 (0x10000) – индикация процента открытия

задвижки вместо процента закрытия на выходе

Q%L;

![]() бит 17 (0x20000) – если задвижка не находится в

одном из крайних положений, выход Q%L

индицирует время (в секундах), оставшееся до закрытия/открытия. В

крайних положениях задвижки Q%L=0;

бит 17 (0x20000) – если задвижка не находится в

одном из крайних положений, выход Q%L

индицирует время (в секундах), оставшееся до закрытия/открытия. В

крайних положениях задвижки Q%L=0;

![]() бит 18 (0x40000) – запрет сброса сигнала на

OPN/CLS (например, для задвижки, которая должна

удерживаться в крайнем положении);

бит 18 (0x40000) – запрет сброса сигнала на

OPN/CLS (например, для задвижки, которая должна

удерживаться в крайнем положении);

![]() бит 20 (0x100000) – при наличии сигнала концевого

выключателя закрытия наличие сигнала муфты не анализируется

(считается, что он есть);

бит 20 (0x100000) – при наличии сигнала концевого

выключателя закрытия наличие сигнала муфты не анализируется

(считается, что он есть);

![]() бит 21 (0x200000) – разрешение анализа сигнала

электрической части (привода). Наличие сигнала анализируется спустя

1 такт пересчета после подачи команды, а если задвижка находится в

интервале (%SdV,

100-%SdV)

– спустя 2 такта;

бит 21 (0x200000) – разрешение анализа сигнала

электрической части (привода). Наличие сигнала анализируется спустя

1 такт пересчета после подачи команды, а если задвижка находится в

интервале (%SdV,

100-%SdV)

– спустя 2 такта;

![]() бит 22 (0x400000) – в режиме импульсных

управляющих сигналов (установлен бит 9) – разрешение генерации

управляющего импульса остановки в случае диагностирования положения

ОТКРЫТО/ЗАКРЫТО по концевому выключателю.

бит 22 (0x400000) – в режиме импульсных

управляющих сигналов (установлен бит 9) – разрешение генерации

управляющего импульса остановки в случае диагностирования положения

ОТКРЫТО/ЗАКРЫТО по концевому выключателю.

Байт 0 (0xFF) выхода ALR (этот байт показывает состояние задвижки) может принимать следующие значения:

![]() 1 – открывается;

1 – открывается;

![]() 2 – закрывается;

2 – закрывается;

![]() 4 – открыта;

4 – открыта;

![]() 8 – закрыта;

8 – закрыта;

![]() 17 (0x11) – остановка при открытии;

17 (0x11) – остановка при открытии;

![]() 18 (0x12) – остановка при закрытии;

18 (0x12) – остановка при закрытии;

![]() 33 (0x21) – открывается в пределах таймаута

концевого выключателя (*);

33 (0x21) – открывается в пределах таймаута

концевого выключателя (*);

![]() 34 (0x22) – закрывается в пределах таймаута

концевого выключателя;

34 (0x22) – закрывается в пределах таймаута

концевого выключателя;

![]() 49 (0x31) – остановка при открытии в пределах

таймаута концевого выключателя;

49 (0x31) – остановка при открытии в пределах

таймаута концевого выключателя;

![]() 50 (0x32) – остановка при закрытии в пределах

таймаута концевого выключателя.

50 (0x32) – остановка при закрытии в пределах

таймаута концевого выключателя.

Байт 1 (0xFF00) выхода ALR указывает на возникновение аварийных ситуаций (аварийные ситуации не контролируются, если они связаны с сигналами, контроль которых заблокирован):

![]() 0 – норма;

0 – норма;

![]() 1 – одновременно присутствуют сигналы концевых

выключателей открытия и закрытия;

1 – одновременно присутствуют сигналы концевых

выключателей открытия и закрытия;

![]() 2 – при открытии не отключился концевой

выключатель закрытия или муфты по истечении времени, заданного с

помощью блока SdV (*);

2 – при открытии не отключился концевой

выключатель закрытия или муфты по истечении времени, заданного с

помощью блока SdV (*);

![]() 3 – при закрытии не отключился концевой

выключатель открытия по истечении времени, заданного с помощью

блока SdV (*);

3 – при закрытии не отключился концевой

выключатель открытия по истечении времени, заданного с помощью

блока SdV (*);

![]() 4 – остановка при открытии по времени (истекли

PT секунд, а сигнала концевого выключателя открытия

нет);

4 – остановка при открытии по времени (истекли

PT секунд, а сигнала концевого выключателя открытия

нет);

![]() 5 – остановка при закрытии по времени (истекли

PT секунд, а сигнала концевого выключателя закрытия и/или

муфты нет);

5 – остановка при закрытии по времени (истекли

PT секунд, а сигнала концевого выключателя закрытия и/или

муфты нет);

![]() 6 – остановка (возможно, задвижка закрыта внешними

средствами);

6 – остановка (возможно, задвижка закрыта внешними

средствами);

![]() 7 – остановка (возможно, задвижка открыта внешними

средствами);

7 – остановка (возможно, задвижка открыта внешними

средствами);

![]() 8 – наличие сигнала электрической части (привода)

при неподвижной задвижке;

8 – наличие сигнала электрической части (привода)

при неподвижной задвижке;

![]() 9 – нет напряжения;

9 – нет напряжения;

![]() 10 – задвижка открыта, но сигнала концевого

выключателя открытия нет;

10 – задвижка открыта, но сигнала концевого

выключателя открытия нет;

![]() 11 – задвижка закрыта, но сигнала концевого

выключателя закрытия нет;

11 – задвижка закрыта, но сигнала концевого

выключателя закрытия нет;

![]() 12 – при закрытой задвижке пропал сигнал концевого

выключателя муфты, а сигнал концевого выключателя закрытия

остался;

12 – при закрытой задвижке пропал сигнал концевого

выключателя муфты, а сигнал концевого выключателя закрытия

остался;

![]() 13 – при закрытой задвижке пропали сигналы

концевых выключателей закрытия и муфты.

13 – при закрытой задвижке пропали сигналы

концевых выключателей закрытия и муфты.

![]() 14 – задвижка движется, а сигнала электрической

части (привода) нет. В этой ситуации: если бит 8 (0x100) CSC

не установлен, сигнал открытия/закрытия не сбрасывается (считается,

что задвижка движется), в противном случае сигнал сбрасывается;

14 – задвижка движется, а сигнала электрической

части (привода) нет. В этой ситуации: если бит 8 (0x100) CSC

не установлен, сигнал открытия/закрытия не сбрасывается (считается,

что задвижка движется), в противном случае сигнал сбрасывается;

![]() 15 – это значение указывает, что блок находится в

режиме отслеживания.

15 – это значение указывает, что блок находится в

режиме отслеживания.

(*) Таймаут (время ожидания отключения) концевого выключателя в отсутствие блока SdV равно 0.1*PT секунд.

Порядок диагностики аварийных ситуаций (при обнаружении ошибки дальнейшая диагностика не выполняется; если анализ соответствующего концевого выключателя блокирован, пункт пропускается):

![]() задвижка остановлена, последнее положение –

"открыто":

задвижка остановлена, последнее положение –

"открыто":

![]() сигнал напряжения;

сигнал напряжения;

![]() сигналы концевых выключателей открытия и закрытия

одновременно;

сигналы концевых выключателей открытия и закрытия

одновременно;

![]() внешнее закрытие;

внешнее закрытие;

![]() сигнал электрической части;

сигнал электрической части;

![]() сигнал концевого выключателя открытия;

сигнал концевого выключателя открытия;

![]() задвижка остановлена, последнее положение –

"закрыто":

задвижка остановлена, последнее положение –

"закрыто":

![]() сигнал напряжения;

сигнал напряжения;

![]() сигналы концевых выключателей открытия и закрытия

одновременно;

сигналы концевых выключателей открытия и закрытия

одновременно;

![]() инверсия сигналов концевых выключателей открытия и

закрытия (внешнее открытие);

инверсия сигналов концевых выключателей открытия и

закрытия (внешнее открытие);

![]() сигнал электрической части;

сигнал электрической части;

![]() сигнал концевого выключателя закрытия;

сигнал концевого выключателя закрытия;

![]() сигнал концевого выключателя муфты;

сигнал концевого выключателя муфты;

![]() сигналы концевых выключателей закрытия и муфты

одновременно;

сигналы концевых выключателей закрытия и муфты

одновременно;

![]() задвижка открывается, время хода истекло:

задвижка открывается, время хода истекло:

![]() сигнал напряжения;

сигнал напряжения;

![]() сигнал концевого выключателя открытия;

сигнал концевого выключателя открытия;

![]() задвижка открывается из положения "закрыто" в

течение времени, которое меньше времени ожидания отключения

концевого выключателя закрытия, сигнал электрической части

отсутствует:

задвижка открывается из положения "закрыто" в

течение времени, которое меньше времени ожидания отключения

концевого выключателя закрытия, сигнал электрической части

отсутствует:

![]() сигнал напряжения;

сигнал напряжения;

![]() генерируется ошибка 14, после чего проверяется

отключение концевого выключателя закрытия. Если в требуемый момент

времени нет отключения концевого выключателя закрытия, генерируется

ошибка 2;

генерируется ошибка 14, после чего проверяется

отключение концевого выключателя закрытия. Если в требуемый момент

времени нет отключения концевого выключателя закрытия, генерируется

ошибка 2;

![]() задвижка закрывается, время хода истекло:

задвижка закрывается, время хода истекло:

![]() сигнал напряжения;

сигнал напряжения;

![]() сигнал концевого выключателя закрытия;

сигнал концевого выключателя закрытия;

![]() задвижка закрывается из положения "открыто" в

течение времени, которое меньше времени ожидания отключения

концевого выключателя открытия, сигнал электрической части

отсутствует:

задвижка закрывается из положения "открыто" в

течение времени, которое меньше времени ожидания отключения

концевого выключателя открытия, сигнал электрической части

отсутствует:

![]() сигнал напряжения;

сигнал напряжения;

![]() генерируется ошибка 14, после чего проверяется

отключение концевого выключателя открытия. Если в требуемый момент

времени нет отключения концевого выключателя открытия, генерируется

ошибка 3.

генерируется ошибка 14, после чего проверяется

отключение концевого выключателя открытия. Если в требуемый момент

времени нет отключения концевого выключателя открытия, генерируется

ошибка 3.

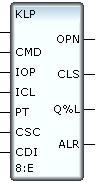

Блок KLP представляет собой модификацию блока ZDV для управления устройством типа "регулирующий клапан". Блок анализирует следующие цифровые сигналы (0 или 1): сигналы концевых выключателей открытия и закрытия, сигнал электрической части (привода) и сигнал о наличии электрического напряжения. Кроме того, блок анализирует аналоговый сигнал в диапазоне 0-100, показывающий реальное положение клапана (0 – полностью открыт, 100 – полностью закрыт).

Вход CMD задает направление движения клапана: положительная величина – открытие, отрицательная – закрытие. При выполнении этих команд на выходе OPN формируется сигнал открытия (значение 1), на выходе CLS – сигнал закрытия (значение 1). В режиме отслеживания неотрицательное значение входа CMD (0-100) задает положение, которое должен занять клапан.

Вход PT используется для задания времени хода клапана (в секундах). Если контроль положения клапана блокирован, блок вычисляет текущее положение клапана и выводит полученное значение на выход Q%L (аналогично ZDV).

На вход CDI подается реальное положение клапана (аналоговый сигнал в диапазоне 0-100, соответствующий проценту закрытия).

Если контроль положения клапана не блокирован, блок не вычисляет положение, и Q%L=CDI.

На вход IOP подаются следующие сигналы:

![]() бит 0 (0x1) – сигнал концевого выключателя

открытия (1 – открыто полностью, 0 – закрыто или открыто не

полностью);

бит 0 (0x1) – сигнал концевого выключателя

открытия (1 – открыто полностью, 0 – закрыто или открыто не

полностью);

![]() бит 3 или 8 (0x8 или 0x100) – сигнал электрической

части (привода) (0 – не работает, 1 – работает);

бит 3 или 8 (0x8 или 0x100) – сигнал электрической

части (привода) (0 – не работает, 1 – работает);

![]() бит 2 или 9 (0x4 или 0x200) – сигнал о наличии

напряжения: 0 – норма, 1 – авария).

бит 2 или 9 (0x4 или 0x200) – сигнал о наличии

напряжения: 0 – норма, 1 – авария).

На вход ICL подаются следующие сигналы:

![]() бит 0 (0x1) – сигнал концевого выключателя

закрытия (1 – закрыто полностью, 0 – открыто или закрыто не

полностью);

бит 0 (0x1) – сигнал концевого выключателя

закрытия (1 – закрыто полностью, 0 – открыто или закрыто не

полностью);

![]() биты 3 и 8 (0x8 и 0x100) – аналоги битов 3 и 8

IOP;

биты 3 и 8 (0x8 и 0x100) – аналоги битов 3 и 8

IOP;

![]() бит 2 или 9 (0x4 или 0x200) – аналоги битов 2 и 9

IOP.

бит 2 или 9 (0x4 или 0x200) – аналоги битов 2 и 9

IOP.

Если на ICL ничего не подано, то ICL = IOP & 6.

Аналогично ZDV, сигналы концевых выключателей имеют более высокий приоритет по сравнению с данными о положении клапана (как вычисленными, так и полученными от устройства).

Установленные в 1 биты входа CSC соответствуют следующим режимам работы блока:

![]() бит 0 (0x1) – блокирование контроля концевого

выключателя открытия;

бит 0 (0x1) – блокирование контроля концевого

выключателя открытия;

![]() бит 1 (0x2) – блокирование контроля концевого

выключателя закрытия;

бит 1 (0x2) – блокирование контроля концевого

выключателя закрытия;

![]() бит 2 (0x4) – блокирование контроля положения

клапана;

бит 2 (0x4) – блокирование контроля положения

клапана;

![]() бит 3 (0x8) – принудительное присваивание выходу

Q%L значения 0 ("открыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

бит 3 (0x8) – принудительное присваивание выходу

Q%L значения 0 ("открыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

![]() бит 4 (0x10) – принудительное присваивание выходу

Q%L значения 100 ("закрыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

бит 4 (0x10) – принудительное присваивание выходу

Q%L значения 100 ("закрыто") при выходе из

аварийной ситуации (т.е. при установленном бите 5);

![]() бит 5 (0x20) – выход из аварийной ситуации. При

возникновении аварийной ситуации при открытии/закрытии

соответствующие выходы (OPN и CLS) принимают значение

0 (процедура прерывается), и блок KLP останавливается. Если

в режиме остановки ошибку устранить (т.е. задать корректное

сочетание значений входов), выполнение процедуры не возобновится, и

признак аварии, сформированный на выходе ALR, сохранится.

Для сброса признака аварии и возобновления выполнения процедуры

нужно установить данный бит в 1. При установке бита 5 возможна

одновременная установка бита 3 (0x8) или бита 4 (0x10) для

выполнения соответствующих функций (одновременная установка битов

3-5 равнозначна установке одного бита 5);

бит 5 (0x20) – выход из аварийной ситуации. При

возникновении аварийной ситуации при открытии/закрытии

соответствующие выходы (OPN и CLS) принимают значение

0 (процедура прерывается), и блок KLP останавливается. Если

в режиме остановки ошибку устранить (т.е. задать корректное

сочетание значений входов), выполнение процедуры не возобновится, и

признак аварии, сформированный на выходе ALR, сохранится.

Для сброса признака аварии и возобновления выполнения процедуры

нужно установить данный бит в 1. При установке бита 5 возможна

одновременная установка бита 3 (0x8) или бита 4 (0x10) для

выполнения соответствующих функций (одновременная установка битов

3-5 равнозначна установке одного бита 5);

![]() бит 6 (0x40) – компенсировать инерционность. В

этом режиме при реверсе к вычисленному положению

добавляется/вычитается половина величины, соответствующей времени

ожидания отключения концевого выключателя (т.е. 5% в

отсутствие SdV);

бит 6 (0x40) – компенсировать инерционность. В

этом режиме при реверсе к вычисленному положению

добавляется/вычитается половина величины, соответствующей времени

ожидания отключения концевого выключателя (т.е. 5% в

отсутствие SdV);

![]() бит 7 (0x80) – перевод в режим отслеживания

состояния клапана по концевым выключателям (аварийные ситуации не

контролируются). Этот режим индицируется значением 15 байта 1

(0x0F00) выхода ALR);

бит 7 (0x80) – перевод в режим отслеживания

состояния клапана по концевым выключателям (аварийные ситуации не

контролируются). Этот режим индицируется значением 15 байта 1

(0x0F00) выхода ALR);

![]() бит 10 (0x400) – блокирование команды

открытия;

бит 10 (0x400) – блокирование команды

открытия;

![]() бит 11 (0x800) – блокирование команды

закрытия.

бит 11 (0x800) – блокирование команды

закрытия.

Если команда открытия (закрытия) блокируется битом 10 (11) STS в момент выполнения, клапан останавливается.

![]() бит 12 (0x1000) – если бит 12 равен 1, клапан

переходит в положение, заданное неотрицательным значением

CMD (режим отслеживания). Скорость перехода определяется

PT;

бит 12 (0x1000) – если бит 12 равен 1, клапан

переходит в положение, заданное неотрицательным значением

CMD (режим отслеживания). Скорость перехода определяется

PT;

![]() бит 16 (0x10000) – индикация процента открытия

вместо процента закрытия на выходе Q%L;

бит 16 (0x10000) – индикация процента открытия

вместо процента закрытия на выходе Q%L;

![]() бит 21 (0x200000) – разрешение анализа сигнала

электрической части (привода).

бит 21 (0x200000) – разрешение анализа сигнала

электрической части (привода).

Байт 0 (0xFF) ALR (этот байт показывает состояние клапана) может принимать следующие значения:

![]() 1 – открывается;

1 – открывается;

![]() 2 – закрывается;

2 – закрывается;

![]() 4 – открыт;

4 – открыт;

![]() 8 – закрыт;

8 – закрыт;

![]() 17 – остановка при открытии (16#11);

17 – остановка при открытии (16#11);

![]() 18 – остановка при закрытии (16#12);

18 – остановка при закрытии (16#12);

Байт 1 (0xFF00) ALR указывает на возникновение аварийных ситуаций (аварийные ситуации не контролируются, если они связаны с сигналами, контроль которых заблокирован):

![]() 0 – норма;

0 – норма;

![]() 1 – одновременно установлены в 1 сигналы концевых

выключателей открытия и закрытия;

1 – одновременно установлены в 1 сигналы концевых

выключателей открытия и закрытия;

![]() 2 – при открытии не отключился концевой

выключатель закрытия по истечении времени, заданного с помощью

блока SdV (*);

2 – при открытии не отключился концевой

выключатель закрытия по истечении времени, заданного с помощью

блока SdV (*);

![]() 3 – при закрытии не отключился концевой

выключатель открытия по истечении времени, заданного с помощью

блока SdV (*);

3 – при закрытии не отключился концевой

выключатель открытия по истечении времени, заданного с помощью

блока SdV (*);

![]() 4 – остановка при открытии по времени (истекли

PT секунд, а сигнала концевого выключателя открытия

нет);

4 – остановка при открытии по времени (истекли

PT секунд, а сигнала концевого выключателя открытия

нет);

![]() 5 – остановка при закрытии по времени (истекли

PT секунд, а сигнала концевого выключателя закрытия

нет);

5 – остановка при закрытии по времени (истекли

PT секунд, а сигнала концевого выключателя закрытия

нет);

![]() 6 – остановка при возникновении ошибки 2

(возможно, клапан закрыт внешними средствами);

6 – остановка при возникновении ошибки 2

(возможно, клапан закрыт внешними средствами);

![]() 7 – остановка при возникновении ошибки 3

(возможно, клапан открыт внешними средствами);

7 – остановка при возникновении ошибки 3

(возможно, клапан открыт внешними средствами);

![]() 8 – наличие сигнала электрической части (привода)

при неподвижном клапане;

8 – наличие сигнала электрической части (привода)

при неподвижном клапане;

![]() 9 – отклонение вычисленного положения клапана от

реального (Q%L от CDI) превышает

максимально допустимое значение, заданное с помощью блока

SdV(*). Данная ошибка детектируется, если при движении

клапана разрешается контроль положения (сбрасывается бит 2

CSC);

9 – отклонение вычисленного положения клапана от

реального (Q%L от CDI) превышает

максимально допустимое значение, заданное с помощью блока

SdV(*). Данная ошибка детектируется, если при движении

клапана разрешается контроль положения (сбрасывается бит 2

CSC);

![]() 10 – клапан открыт, но сигнала концевого

выключателя открытия нет;

10 – клапан открыт, но сигнала концевого

выключателя открытия нет;

![]() 11 – клапан закрыт, но сигнала концевого

выключателя закрытия нет;

11 – клапан закрыт, но сигнала концевого

выключателя закрытия нет;

![]() 12 – нет напряжения;

12 – нет напряжения;

![]() 14 – клапан движется, а сигнала электрической

части (привода) нет;

14 – клапан движется, а сигнала электрической

части (привода) нет;

![]() 15 – это значение указывает, что блок находится в

режиме отслеживания.

15 – это значение указывает, что блок находится в

режиме отслеживания.

(*) Таймаут (время ожидания отключения) концевого выключателя в отсутствие блока SdV равно 0.1*PT секунд. Максимально допустимое отклонение Q%L от CDI в отсутствие блока SdV равно 1000/PT.

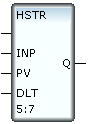

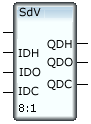

Настройки параметров задвижек и клапанов (SdV)

По значениям выходов блока SdV устанавливаются критерии аварийных ситуаций для блоков KLP и ZDV:

QDH – по значению этого выхода устанавливается максимально допустимое отклонение вычисленного положения клапана от реального: при |CDI-Q%L|>=100*QDH/PT формируется ошибка 9 и процедура открытия/закрытия клапана прерывается (см. описание блока KLP). QDH=IDH, если 0<=IDH<=100; QDH=0, если IDH>100 или IDH<0, а также если вход IDH не определен. При QDH=0 ошибка 9 формируется даже при CDI=Q%L;

QDO – если при закрытии задвижки или клапана из положения "открыто" по истечении QDO*PT секунд не отключился концевой выключатель открытия, формируется ошибка 3, и процедура закрытия прерывается (см. описание блоков ZDV и KLP). QDO=IDO, если 0.1<=IDO<=0.5; QDO=0.1, если IDO<0.1 или IDO>0.5, а также если вход IDO не определен;

QDC – если при открытии задвижки или клапана из положения "закрыто" по истечении (1-IDС)*PT секунд не отключились концевые выключатели закрытия и муфты, формируется ошибка 2, и процедура открытия прерывается (см. описание блоков ZDV и KLP). QDC=IDC, если 0.5<=IDC<=0.9; QDC=0.9, если IDC<0.5 или IDC>0.9, а также если вход IDC не определен.

После отработки блока SdV для всех блоков KLP и ZDV на текущем узле будут использоваться установленные им настройки. Они будут изменены после отработки следующего блока SdV или следующего пересчета этого блока с измененными значениями его входов.

Данный блок с соединенными выходом Q и входом IQ выполняет сглаживание входного сигнала (INP) звеном второго порядка. Постоянная времени сглаживания определяется входом PT. Значение этого входа задает количество тактов, за которое выходное значение сравняется с входным при условии неизменности последнего после первого изменения.

Алгоритм сглаживания выглядит следующим образом (i обозначает текущий такт пересчета).

IF (INPi<>INPi-1)&&(N==PT) THEN N:=1

IF N<PT THEN Qi:=IQi+N*(INPi-IQi)/PT; N:=N+1

ELSE Qi:=INPi

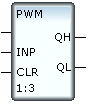

Широтно-импульсная модуляция (ШИМ) - вид импульсной модуляции, при которой под действием модулирующего сигнала изменяется длительность (ширина) импульсов при постоянной частоте их следования.

При подаче на вход INP модулирующего сигнала на выходе блока формируется широтно-модулированный импульсный сигнал единичной амплитуды с частотой следования импульсов 1/2t, где t – период пересчета блока.

Длина импульса округляется до величины, кратной периоду пересчета блока. Для компенсации возникающей в связи с этим ошибки разности между округленной и истинной длиной импульсов суммируются. Когда абсолютное значение этой суммы превышает длительность одного такта, один такт добавляется или вычитается из длины очередного импульса. Подача на вход CLR отличной от нуля величины сбрасывает накопленную ошибку.

Значение модулирующего сигнала (INP) не должно выходить за границы диапазона [-100, 100], максимальная частота должна быть много меньше частоты пересчета блока.

При положительном значении входной величины импульсы формируются на выходе QH (при этом QL=0), при отрицательном – на выходе QL (при этом QH=0).

На выходе этого блока формируется последовательность импульсов с единичной амплитудой, длительностью PT1 тактов пересчета и периодом следования (PT1 + PT0) тактов.

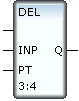

Данный блок воспроизводит на выходе значение входа INP. Однако при равенстве входа нулю значение выхода перестает меняться на время задержки, задаваемой значением входа PT (в тактах пересчета).

Управление устройством типа ’двигатель’ (MOTOR)

Данный блок предназначен для управления одно- или двухскоростным мотором, снабженным входом (входами) включения и выключения. Кроме того, мотор может быть оборудован следующими цифровыми датчиками: датчиком включения на скорости 1, датчиком включения на скорости 2, датчиком выключения и датчиком нагрузки. По сигналам этих датчиков блок MOTOR может анализировать состояние мотора.

Блок MOTOR может находиться в следующих режимах: WORK (работа), RESERVE (резерв), REPAIR (ремонт) и ERROR (ошибка). Режим RESERVE имеет разновидности: ACTIVE_RESERVE – резерв с возможностью включения, PASSIVE_RESERVE – резерв без возможности включения

Блок имеет следующие функциональные входы:

![]() CMD – команда управления:

CMD – команда управления:

![]() 1 – включить на скорости 1;

1 – включить на скорости 1;

![]() 2 – выключить;

2 – выключить;

![]() 4 – в ACTIVE_RESERVE: включить на скорости 1;

4 – в ACTIVE_RESERVE: включить на скорости 1;

![]() 8 – включить на скорости 2;

8 – включить на скорости 2;

![]() STS – перевод в нужный режим:

STS – перевод в нужный режим:

![]() 0 – блокировка команд CMD;

0 – блокировка команд CMD;

![]() 2 – разрешение команд CMD;

2 – разрешение команд CMD;

![]() 3 – перевод в PASSIVE_RESERVE;

3 – перевод в PASSIVE_RESERVE;

![]() 4 – перевод в REPAIR;

4 – перевод в REPAIR;

![]() 5 – перевод в ERROR;

5 – перевод в ERROR;

![]() 6 – сброс ошибок, предыдущий режим

запоминается;

6 – сброс ошибок, предыдущий режим

запоминается;

![]() 7 – сброс ошибок, предыдущий режим не

запоминается;

7 – сброс ошибок, предыдущий режим не

запоминается;

![]() 8 – перевод в ACTIVE_RESERVE;

8 – перевод в ACTIVE_RESERVE;

![]() 9 – в PASSIVE_RESERVE: перевод в

ACTIVE_RESERVE.

9 – в PASSIVE_RESERVE: перевод в

ACTIVE_RESERVE.

![]() END – установленные в 1 биты этого входа

интерпретируются следующим образом:

END – установленные в 1 биты этого входа

интерпретируются следующим образом:

![]() бит 0 – мотор включен на скорости 1;

бит 0 – мотор включен на скорости 1;

![]() бит 1 – мотор выключен;

бит 1 – мотор выключен;

![]() бит 2 – наличие нагрузки;

бит 2 – наличие нагрузки;

![]() бит 3 – мотор включен на скорости 2;

бит 3 – мотор включен на скорости 2;

![]() бит 4 – не анализировать сигнал датчика включения

на скорости 1;

бит 4 – не анализировать сигнал датчика включения

на скорости 1;

![]() бит 5 – не анализировать сигнал датчика

выключения;

бит 5 – не анализировать сигнал датчика

выключения;

![]() бит 6 – не анализировать сигнал датчика

нагрузки;

бит 6 – не анализировать сигнал датчика

нагрузки;

![]() бит 7 – не анализировать сигнал датчика включения

на скорости 2;

бит 7 – не анализировать сигнал датчика включения

на скорости 2;

![]() dT – максимальная длительность сигналов,

генерируемых на выходах ON и OFF (в секундах);

dT – максимальная длительность сигналов,

генерируемых на выходах ON и OFF (в секундах);

![]() ALR – ненулевое значение этого входа

интерпретируется как команда аварийного выключения мотора, при этом

блок переводится в режим ERROR. Эта команда имеет наивысший

приоритет;

ALR – ненулевое значение этого входа

интерпретируется как команда аварийного выключения мотора, при этом

блок переводится в режим ERROR. Эта команда имеет наивысший

приоритет;

![]() T – в течение (dT+T) секунд с

момента подачи команды блок ожидает прихода подтверждающих сигналов

датчиков (см. описание выхода ERR);

T – в течение (dT+T) секунд с

момента подачи команды блок ожидает прихода подтверждающих сигналов

датчиков (см. описание выхода ERR);

![]() CHK – установленные в 1 биты

интерпретируются следующим образом (все команды CHK имеют

более высокий приоритет по сравнению с аналогичными командами

других входов блока):

CHK – установленные в 1 биты

интерпретируются следующим образом (все команды CHK имеют

более высокий приоритет по сравнению с аналогичными командами

других входов блока):

![]() биты 0, 1, 2, 3 – ручная команда

включения/выключения;

биты 0, 1, 2, 3 – ручная команда

включения/выключения;

![]() бит 5 (0x20) – аналог STS(вход)=7;

бит 5 (0x20) – аналог STS(вход)=7;

![]() бит 6 (0x40) – разрешение анализа сигнала датчика

нагрузки;

бит 6 (0x40) – разрешение анализа сигнала датчика

нагрузки;

![]() бит 7 (0x80) – отслеживание по сигналам датчиков

включения и выключения;

бит 7 (0x80) – отслеживание по сигналам датчиков

включения и выключения;

![]() бит 8 (0x100) – установка бита 7 (0x80) в случае

ошибки;

бит 8 (0x100) – установка бита 7 (0x80) в случае

ошибки;

![]() бит 10 (0x400) – блокировка команды включения по

CHK;

бит 10 (0x400) – блокировка команды включения по

CHK;

![]() бит 9 (0x200) – аналог STS(вход)=6;

бит 9 (0x200) – аналог STS(вход)=6;

![]() бит 11 (0x800) – блокировка команды выключения по

CHK;

бит 11 (0x800) – блокировка команды выключения по

CHK;

![]() бит 12 (0x1000) – установка бита 6 (0x40) выхода

STS (в режиме WORK этот бит равен 0);

бит 12 (0x1000) – установка бита 6 (0x40) выхода

STS (в режиме WORK этот бит равен 0);

![]() бит 13 (0x2000) – разрешение команд

CMD;

бит 13 (0x2000) – разрешение команд

CMD;

![]() бит 14 (0x4000) – разрешение отработки команды

CMD=1 в резерве;

бит 14 (0x4000) – разрешение отработки команды

CMD=1 в резерве;

![]() бит 15 (0x8000) – запрет STS(выход)=5

(кроме прямой команды ALR).

бит 15 (0x8000) – запрет STS(выход)=5

(кроме прямой команды ALR).

При использовании с блоком SBRK: при установке бита 15 необходимо установить бит 8.

Выходы блока имеют следующее назначение:

![]() STS – коды, индицируемые на этом выходе,

соответствуют следующим состояниям (при ручном управлении по

CHK дополнительно устанавливается бит 4 (0x10)

STS):

STS – коды, индицируемые на этом выходе,

соответствуют следующим состояниям (при ручном управлении по

CHK дополнительно устанавливается бит 4 (0x10)

STS):

![]() 0 – инициализация;

0 – инициализация;

![]() 1 – включен на скорости 1;

1 – включен на скорости 1;

![]() 2 – выключен;

2 – выключен;

![]() 3 – ACTIVE_RESERVE, выключен;

3 – ACTIVE_RESERVE, выключен;

![]() 4 – REPAIR;

4 – REPAIR;

![]() 5 – ERROR;

5 – ERROR;

![]() 6 – выключен и запрещены команды

(STS(вход)=0 и нет CHK=0x2000);

6 – выключен и запрещены команды

(STS(вход)=0 и нет CHK=0x2000);

![]() 7 – включен и запрещены команды;

7 – включен и запрещены команды;

![]() 8 – включен на скорости 2;

8 – включен на скорости 2;

![]() 9 – процесс включения на скорости 1;

9 – процесс включения на скорости 1;

![]() 10 – процесс выключения;

10 – процесс выключения;

![]() 11 – PASSIVE_RESERVE;

11 – PASSIVE_RESERVE;

![]() 12 – холостой ход;

12 – холостой ход;

![]() 13 – процесс включения на скорости 2;

13 – процесс включения на скорости 2;

![]() 14 – перевод в ACTIVE_RESERVE с выключением;

14 – перевод в ACTIVE_RESERVE с выключением;

![]() 15 – ACTIVE_RESERVE, включен.

15 – ACTIVE_RESERVE, включен.

![]() ON – в бите 0 этого выхода генерируются

сигнал включения на скорости 1, в бите 2 – сигнал включения на

скорости 2;

ON – в бите 0 этого выхода генерируются

сигнал включения на скорости 1, в бите 2 – сигнал включения на

скорости 2;

![]() OFF – на этом выходе генерируется сигнал

выключения;

OFF – на этом выходе генерируется сигнал

выключения;

![]() ERR – характеристика аварийной

ситуации:

ERR – характеристика аварийной

ситуации:

![]() 1 – одновременные сигналы любых двух или всех трех

датчиков включения и выключения;

1 – одновременные сигналы любых двух или всех трех

датчиков включения и выключения;

![]() 2 – мотор выключен внешними средствами (т.е. не с

помощью блока MOTOR);

2 – мотор выключен внешними средствами (т.е. не с

помощью блока MOTOR);

![]() 3 – мотор включен внешними средствами (на любой

скорости);

3 – мотор включен внешними средствами (на любой

скорости);

![]() 4 – в течение (dT+T) секунд

после подачи команды выключения не пришел подтверждающий сигнал от

датчика выключения;

4 – в течение (dT+T) секунд

после подачи команды выключения не пришел подтверждающий сигнал от

датчика выключения;

![]() 5 – в течение (dT+T) секунд

после подачи команды включения не пришел подтверждающий сигнал от

датчика включения;

5 – в течение (dT+T) секунд

после подачи команды включения не пришел подтверждающий сигнал от

датчика включения;

![]() 6 – в течение dT секунд после подачи

команды включения не сброшен сигнал датчика выключения;

6 – в течение dT секунд после подачи

команды включения не сброшен сигнал датчика выключения;

![]() 7 – в течение dT секунд после подачи

команды выключения не сброшен сигнал датчика включения;

7 – в течение dT секунд после подачи

команды выключения не сброшен сигнал датчика включения;

![]() 8 – блок переведен в режим ERROR по STS=5.

Значение 8 индицируется также при любой ошибке кроме тех, которые

индицируются другими кодами ERR;

8 – блок переведен в режим ERROR по STS=5.

Значение 8 индицируется также при любой ошибке кроме тех, которые

индицируются другими кодами ERR;

![]() 9 – отработана команда аварийного выключения

двигателя ALR<>0;

9 – отработана команда аварийного выключения

двигателя ALR<>0;

![]() 10 – при включенном моторе (на любой скорости)

исчезла нагрузка;

10 – при включенном моторе (на любой скорости)

исчезла нагрузка;

![]() 11 – нет подтверждающего сигнала ни от одного из

трех датчиков включения и выключения;

11 – нет подтверждающего сигнала ни от одного из

трех датчиков включения и выключения;

![]() 12 – мотор выключен или в резерве и появилась

нагрузка;

12 – мотор выключен или в резерве и появилась

нагрузка;

![]() 14 – скорость изменена внешними средствами.

14 – скорость изменена внешними средствами.

Управление группой устройств типа ’двигатель’ (SBRK)

Данная FBD-программа управляет группой из 3 насосов (два рабочих и один резервный), поддерживающих давление P в трубопроводе в диапазоне [LOW, HIGH].

В программе входы S0…S2 блока SBRK соединены с выходами STS, а выходы QS0…QS2 – с входами STS блоков MOTOR. При этом вход Si и выход QSi (т.е., имеющие один и тот же номер i) соединены соответственно с выходом STS и входом STS одного и того же блока MOTOR. По номеру i=0…2 блок SBRK идентифицирует управляемое устройство.

Выход CMD блока SBRK соединен с входами CMD блоков MOTOR.

Установленные в 1 биты CNT интерпретируются следующим образом:

![]() бит 0 (0x1) – P>=HIGH;

бит 0 (0x1) – P>=HIGH;

![]() бит 1 (0x2) – P<=LOW;

бит 1 (0x2) – P<=LOW;

![]() бит 2 (0x4) –

бит 2 (0x4) –

![]() бит 4 (0x10) – запрет анализа HIGH;

бит 4 (0x10) – запрет анализа HIGH;

![]() бит 5 (0x20) – запрет анализа LOW;

бит 5 (0x20) – запрет анализа LOW;

![]() бит 6 (0x40) –

бит 6 (0x40) –

CMD – команда управления (может быть импульс): 1 – включить, 2 – выключить. SBRK запоминает последнюю команду.

Алгоритм работы:

![]() по команде "включить" включаются 2 мотора, начиная

с нулевого. Насос, выбранный в качестве резервного (находится в

режиме PASSIVE_RESERVE), не включается;

по команде "включить" включаются 2 мотора, начиная

с нулевого. Насос, выбранный в качестве резервного (находится в

режиме PASSIVE_RESERVE), не включается;

![]() при P>=HIGH: насос, выбранный в качестве

резервного, переводится в ACTIVE_RESERVE;

при P>=HIGH: насос, выбранный в качестве

резервного, переводится в ACTIVE_RESERVE;

![]() при P<=LOW: если хотя бы один насос включен,

включается насос, находящийся в ACTIVE_RESERVE;

при P<=LOW: если хотя бы один насос включен,

включается насос, находящийся в ACTIVE_RESERVE;

![]() по команде "выключить" включенные насосы

выключаются, а насос в ACTIVE_RESERVE переводится в

PASSIVE_RESERVE.

по команде "выключить" включенные насосы

выключаются, а насос в ACTIVE_RESERVE переводится в

PASSIVE_RESERVE.

Вход IST используется для управления отдельными устройствами. Значения битов 0-3 задают команды 3, 8 и 9, аналогичные командам входа STS блока MOTOR. Номер устройства (блока MOTOR), которое должно выполнить такую команду, задается значением битов 4-7 IST.

Значения байта 0 (0xFF) ERR индицируют следующие ситуации:

![]() 0 – последняя команда – выключить, не выбран

резерв;

0 – последняя команда – выключить, не выбран

резерв;

![]() 1 – команда – включить, не выбран резерв;

1 – команда – включить, не выбран резерв;

![]() 2 – команда – выключить, выбран резерв;

2 – команда – выключить, выбран резерв;

![]() 3 – команда – включить, выбран резерв;

3 – команда – включить, выбран резерв;

![]() 4 – команда – выключить, резерв выбран и переведен

(была ситуация P>=HIGH);

4 – команда – выключить, резерв выбран и переведен

(была ситуация P>=HIGH);

![]() 5 – команда – включить, резерв выбран и

переведен;

5 – команда – включить, резерв выбран и

переведен;

![]() 6 – ошибка;

6 – ошибка;

![]() 7 – ошибка;

7 – ошибка;

![]() 8 – ошибка;

8 – ошибка;

![]() 9 – требуется включить резерв, а резерв был только

выбран, но не переведен;

9 – требуется включить резерв, а резерв был только

выбран, но не переведен;

![]() 10 – ошибка;

10 – ошибка;

![]() 11 – команда – включить, требуется включить

резерв;

11 – команда – включить, требуется включить

резерв;

![]() 12 – все выключены, требуется включить резерв;

12 – все выключены, требуется включить резерв;

![]() 13 – все включены;

13 – все включены;

![]() 14 – все неисправны;

14 – все неисправны;

![]() 15 – нет подключенных блоков MOTOR (или они

блокируют команды).

15 – нет подключенных блоков MOTOR (или они

блокируют команды).

Биты байта 1 (0xFF00) ERR, установленные в 1, индицируют следующие ситуации:

![]() бит 8 (0x100) – невыполнимая команда включения

(нет блоков для включения),

бит 8 (0x100) – невыполнимая команда включения

(нет блоков для включения),

![]() бит 9 (0x200) – обнаружено устройство с ручным

управлением;

бит 9 (0x200) – обнаружено устройство с ручным

управлением;

![]() бит 10 (0x400) – некорректная команда

IST.

бит 10 (0x400) – некорректная команда

IST.

Зона нечувствительности 2 (DZONE2)

Данный блок работает по следующему алгоритму:

![]() Q = INP – DLT,

если INP > DLT;

Q = INP – DLT,

если INP > DLT;

![]() Q = INP + DLT,

если INP < - DLT;

Q = INP + DLT,

если INP < - DLT;

![]() Q = 0, если -

DLT < INP < DLT.

Q = 0, если -

DLT < INP < DLT.

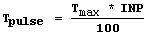

Данный блок выполняет ШИМ-преобразование входного сигнала (INP) по следующему алгоритму:

![]() если |INP| > 100, то |INP| =

100;

если |INP| > 100, то |INP| =

100;

![]() длительность импульсов (амплитуда равна 1) и

длительность промежутков между импульсами определяются по

формулам:

длительность импульсов (амплитуда равна 1) и

длительность промежутков между импульсами определяются по

формулам:

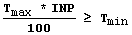

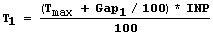

, если

, если

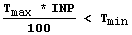

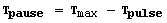

Если  , импульс

не генерируется;

, импульс

не генерируется;

Tmax – время хода устройства; значения Tmin и Tmax задаются в секундах;

![]() для учета люфта устройства предусмотрен вход

Gap. Значение нулевого байта Gap

(Gap0) задает

уширение первого генерируемого импульса при изменении знака

INP с минуса на плюс, значение первого байта Gap

(Gap1) –

уширение первого импульса при изменении знака INP с плюса на

минус. Целое значение байта интерпретируется как число десятков

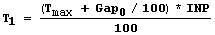

миллисекунд. Таким образом, длительность первого импульса при

изменении знака INP с минуса на плюс определяется по

формуле:

для учета люфта устройства предусмотрен вход

Gap. Значение нулевого байта Gap

(Gap0) задает

уширение первого генерируемого импульса при изменении знака

INP с минуса на плюс, значение первого байта Gap

(Gap1) –

уширение первого импульса при изменении знака INP с плюса на

минус. Целое значение байта интерпретируется как число десятков

миллисекунд. Таким образом, длительность первого импульса при

изменении знака INP с минуса на плюс определяется по

формуле:

Длительность первого импульса при изменении знака INP с плюса на минус определяется по формуле:

Для разрешения использования Gap0 нужно установить бит 8 Mode. Для разрешения использования Gap1 нужно установить бит 9 Mode.

Если INP > 0, импульсы формируются на выходе Up, в противном случае – на выходе Dn;

![]() если INP меняет знак, соответствующий выход

обнуляется, и генерируется импульс на другом выходе;

если INP меняет знак, соответствующий выход

обнуляется, и генерируется импульс на другом выходе;

![]() если INP изменяется с сохранением знака, то

возможны два случая:

если INP изменяется с сохранением знака, то

возможны два случая:

![]()

- если изменение произошло при генерации импульса, длительность импульса увеличивается;

- если изменение произошло в паузе, генерируется импульс (приоритет 1);

![]()

- если изменение произошло при генерации импульса, длительность импульса уменьшается;

- если изменение произошло в паузе, длительность паузы увеличивается;

![]() если бит 0 Mode равен 1, блокируется выдача

сигнала на выход Up;

если бит 0 Mode равен 1, блокируется выдача

сигнала на выход Up;

![]() если бит 1 Mode равен 1, блокируется выдача

сигнала на выход Dn;

если бит 1 Mode равен 1, блокируется выдача

сигнала на выход Dn;

![]() если бит 2 Mode равен 1, блокируется выдача

сигналов на Up и Dn;

если бит 2 Mode равен 1, блокируется выдача

сигналов на Up и Dn;

![]() если бит 3 Mode равен 0, то биты 0 и 1

Mode, кроме того, блокируют ручные команды, если 1 – не

блокируют;

если бит 3 Mode равен 0, то биты 0 и 1

Mode, кроме того, блокируют ручные команды, если 1 – не

блокируют;

![]() если значение битов 4-7 (0xF0) Mode равно

a>0, то при изменении знака INP выходы Up и

Dn принимают значение 0 на a тактов пересчета;

если значение битов 4-7 (0xF0) Mode равно

a>0, то при изменении знака INP выходы Up и

Dn принимают значение 0 на a тактов пересчета;

![]() если значение битов 10 и 11 (0xC00) Mode

равно 3, на выходе вместо "длинного" импульса генерируется

последовательность импульсов минимальной длительности. Если

значение битов равно 1, в течение последних x% длительности

"длинного" импульса на выходе генерируется последовательность

импульсов минимальной длительности (по умолчанию x=5). Если

значение битов равно 2, последовательность импульсов минимальной

длительности генерируется на выходе в том случае, если

INP<k*Tmax

(по умолчанию k=0.05). С помощью файла *.cnf (ключи

IREGPR01 и IREGPR02) можно задать другие x и

k для этого режима;

если значение битов 10 и 11 (0xC00) Mode

равно 3, на выходе вместо "длинного" импульса генерируется

последовательность импульсов минимальной длительности. Если

значение битов равно 1, в течение последних x% длительности

"длинного" импульса на выходе генерируется последовательность

импульсов минимальной длительности (по умолчанию x=5). Если

значение битов равно 2, последовательность импульсов минимальной

длительности генерируется на выходе в том случае, если

INP<k*Tmax

(по умолчанию k=0.05). С помощью файла *.cnf (ключи

IREGPR01 и IREGPR02) можно задать другие x и

k для этого режима;

![]() присвоение 1 биту 12 (0x1000) Mode в ручном

режиме является командой выработки импульса минимальной

длительности на выходе Up;

присвоение 1 биту 12 (0x1000) Mode в ручном

режиме является командой выработки импульса минимальной

длительности на выходе Up;

![]() присвоение 1 биту 13 (0x2000) Mode в ручном

режиме является командой выработки импульса минимальной

длительности на выходе Dn;

присвоение 1 биту 13 (0x2000) Mode в ручном

режиме является командой выработки импульса минимальной

длительности на выходе Dn;

![]() присвоение 1 биту 14 (0x4000) Mode

переводит блок в ручной режим, алгоритм расчета импульса

отключается, Up=Dn=0;

присвоение 1 биту 14 (0x4000) Mode

переводит блок в ручной режим, алгоритм расчета импульса

отключается, Up=Dn=0;

![]() присвоение 1 биту 15 (0x8000) Mode является

командой рестарта алгоритма блока.

присвоение 1 биту 15 (0x8000) Mode является

командой рестарта алгоритма блока.

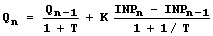

Реальное дифференцирование (RDIF)

Данный блок работает по следующему алгоритму (n – номер такта пересчета):

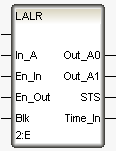

Если бит 11 (0x800) Blk равен 0, биты 0-7 выхода STS индицируют состояния по выходу Out_A0, а биты 8-15 – состояния по выходу Out_A1.

Если бит 11 (0x800) Blk равен 1, биты 0-7 выхода STS индицируют состояния по выходу Out_A0 (состояния по Out_A1 не индицируются).

Установленные в 1 биты выхода STS индицируют следующие состояния:

![]() Бит 0, 0x1 (бит 8, 0x100) – выведено;

Бит 0, 0x1 (бит 8, 0x100) – выведено;

![]() Бит 1, 0x2 (бит 9, 0x200) – введено;

Бит 1, 0x2 (бит 9, 0x200) – введено;

![]() Бит 2, 0x4 (бит 10, 0x400) – выведено и защита

сработала;

Бит 2, 0x4 (бит 10, 0x400) – выведено и защита

сработала;

![]() Бит 3, 0x8 (бит 11, 0x800) – введено и защита

сработала;

Бит 3, 0x8 (бит 11, 0x800) – введено и защита

сработала;

![]() Бит 4, 0x10 (бит 12, 0x1000) – выведено и

блокировка;

Бит 4, 0x10 (бит 12, 0x1000) – выведено и

блокировка;

![]() Бит 5, 0x20 (бит 13, 0x2000) – введено и

блокировка;

Бит 5, 0x20 (бит 13, 0x2000) – введено и

блокировка;

![]() Бит 6, 0x40 (бит 14, 0x4000) – выведено,

блокировка и защита сработала;

Бит 6, 0x40 (бит 14, 0x4000) – выведено,

блокировка и защита сработала;

![]() Бит 7, 0x80 (бит 15, 0x 8000) – введено,

блокировка и защита сработала.

Бит 7, 0x80 (бит 15, 0x 8000) – введено,

блокировка и защита сработала.

Состояние по умолчанию – STS=0.

Введение – En_In=1 (уровень или импульс).

Выведение – En_Out=1 (уровень или импульс).

Требование защиты – In_A=1.

Назначение битов Blk:

![]() бит 0 – 0 – защита не заблокирована, 1 –

заблокирована;

бит 0 – 0 – защита не заблокирована, 1 –

заблокирована;

![]() бит 3 (0x8) –

Out_A1=Out_A0

принудительно;

бит 3 (0x8) –

Out_A1=Out_A0

принудительно;

![]() бит 8 (0x100) – если защита сработала, 1

генерируется на Out_A0 (если бит 8 равен 0)

или на Out_A1 (если бит 8 равен 1);

бит 8 (0x100) – если защита сработала, 1

генерируется на Out_A0 (если бит 8 равен 0)

или на Out_A1 (если бит 8 равен 1);

![]() бит 9 (0x200) – если 1,

Out_A1=Out_A0=0 при

In_A=0 (память отключена);

бит 9 (0x200) – если 1,

Out_A1=Out_A0=0 при

In_A=0 (память отключена);

![]() бит 10 (0x400) – если 1, требование защиты

игнорируется, In_A автоматически

обнуляется;

бит 10 (0x400) – если 1, требование защиты

игнорируется, In_A автоматически

обнуляется;

![]() бит 11 (0x800) – режим STS (см. выше);

бит 11 (0x800) – режим STS (см. выше);

![]() биты 16-23 (0xFF0000) – значение этих битов задает

задержку срабатывания (в секундах).

биты 16-23 (0xFF0000) – значение этих битов задает

задержку срабатывания (в секундах).

Выходы Out_A1 и Out_A0 принимают значение 1 в том случае, если In_A=1, En_In=1, защита не заблокирована и истекло время задержки.

В Time_In записывается время появления 1 на выходе Out_A0/Out_A1.

Out_A0/Out_A1 сохраняет значение 1 пока En_Out=0.

Блокировка не обнуляет Out_A0/Out_A1.

Зарезервирован.